# БЕЗЛИЦЕНЗИОННЫЙ ВЫСОКОСКОРОСТНОЙ АЦП OT TEXAS INSTRUMENTS

Компания Texas Instruments (TI) выпускает широкий ассортимент аналогово-цифровых преобразователей (АЦП), удовлетворяющих требованиям различных промышленных и военных применений. Одним из перспективных и востребованных направлений этого сектора являются высокоскоростные АЦП и интегральные системы на их основе. Областью применения служат радиолокационные системы, цифровые осциллографы, широкополосные цифровые приемники, в том числе многоканальные приемники базовых станций сотовой телефонии.

Интегральная система LM97937, разработанная TI, ориентирована на применение в высокопроизводительных и многофункциональных высокочастотных цифровых приемных устройствах. Структура микросхемы содержит два ядра скоростных АЦП flash-типа, работающих с частотой выборок 370 МГц, буферные входные усилители для аналоговых сигналов и высокоточной глобальной синхронизации.

#### Особенности LM97937

Особенностью устройства является наличие двух блоков цифровой пост-обработки выходных сигналов с ядер АЦП для цифровой фильтрации сигналов и улучшения базового параметра любых ВЧ приемных устройств — отношения сигнал/шум.

LM97937 является микросхемой двухканального АЦП со скоростью преобразования 370 МГц, обеспечивающего передачу данных через выходной интерфейс JESD204B со скоростью до 7,4 Гбит/с. Цифровая фильтрация сигнала после ядер АЦП осуществляется с целью повышения соотношения сигнал/шум и производится на встроенных DSP-модулях с конфигурируемыми пользователем параметрами. По выбору пользователя в DSP-модулях могут использоваться алгоритмы фильтрации SNR Boost или Bit Burst. Технология SNR Boost с формированием окна спектра рабочего поддиапазона позволяет значительно улучшить помехоустойчивость на промежуточной частоте. А технология Bit Burst обеспечивает временное и периодическое увеличение разрешения от 9 до 14 разрядов. Выбор нужного алгоритма производит сам разработчик, исходя из особенностей применения интегрального приемного устройства, характерных шумов входного сигнала и используемых типов модуляции.

Второй особенностью микросхемы является использование в модуле последовательного высокоскоростного выходного интерфейса нового поколения по стандарту JESD204B, который обеспечивает высокую надежность передачи данных потребителю, а также уменьшение площади, занимаемой шинами интерфейса на печатной плате.

Интегрированный входной буфер позволяет снизить шум зарядовых выбросов (charge kick-back noise) и упрощает системный уровень проектирования усилителя, ФНЧ, а также согласование импеданса. С помощью делителя частоты сэмплирования производится подстройка скважности импульсов в соответствии с конфигурируемой фазой выборки и упрощения системы тактирования АЦП.

#### Основные характеристики

Отметим наиболее важные характеристики устройства:

- скорость преобразования до 370 МГц;

- разрешение в двух режимах низкое (Low-Res) 9 бит и высокое (High-Res) 14 бит;

- диапазон входных сигналов 1,7 В «пик-пик»;

- потребляемая мощность 876 мВт/канал;

- буферизация аналоговых входных данных;

- интегральный источник опорного напряжения без внешних компонентов;

- программируемый сигнал тактирования для сэмплирования с делителями частоты (коэффициенты 1, 2, 4, 8);

- выходной интерфейс JESD204B подкласс 1;

- скорость передачи по каждому «лаи́ну» до 7,4 Гбит/с;

- программируемое число «лаи́нов» на канал один или

- управляющий интерфейс четырехпроводной SPI с возможными уровнями сигналов 1,2/1,8/2,5/3,3 В;

- корпус QFN-56 8x8 мм, толщина 0,5 мм.

# Основные области применения

- ВЧ система сэмплирования по промежуточной частоте приемников:

- приемники многочастотных базовых станций сотовой связи GSM/EDGE, CDMA2000, UMTS, LTE и Wi-Max;

- многофункциональные и мультидиапазонные приемники;

- система цифровой коррекции предыскажений в ВЧ приемных трактах.

#### Принципы работы в различных режимах

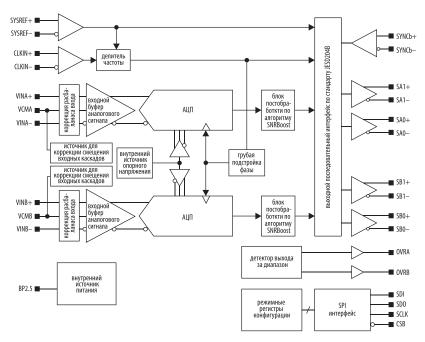

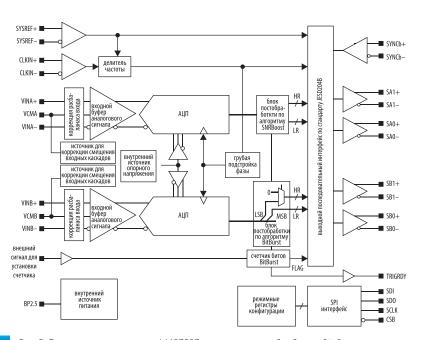

На рисунках 1 и 2 показаны структурные схемы микросхемы LM97937 при работе в режимах SNR Boost и Bit Burst.

Рис. 1. Блок-схема микросхемы LM97937, сконфигурированная для обработки SNR Boost

Рис. 2. Блок-схема микросхемы LM97937 в режиме постобработки Bit Burst

Как можно заметить при сравнении обеих схем, различие их заключается в разных режимах постобработки после ядер АЦП и, соответственно, реализации при обработке сигналов по двум различным алгоритмам. В остальном структуры идентичны и работа тоже.

Сигналы Over-range и Bit Burst Triggering являются внешними и предназначены для мониторинга статуса для организации соответствующей обратной связи воздействия на обработку сигнала. По умолчанию в установках режим коррекции сме-

щения по постоянному напряжению отключен, но может быть включен программно через управляющий интерфейс, если требуется убрать смещение на выходе АЦП ядра. Обработанные данные поступают в модуль интерфеи́са JESD204B, где данные фреимируются, кодируются и преобразуются в последовательный поток для передачи через одну или две дифференциальные линии на канал. Последовательные потоки данных передаютсякпотребителюсигналапосредством конфигурируемых высокоскоростных передатчиков. Сигнал синхронизации сэмплирования образуется из входного сигнала, поступающего через вход CLKIN на вход малошумящего приемника, после преобразования с выхода делителя частоты. Модуль грубой подстройки фазы (Coarse Phase Adjustment) предназначен для управления фазой сигнала сэмплирования. Сигналы со входов CLKIN, SYSREF и SYNCb обеспечивают синхронизацию работы АЦП и выходного интерфейса IESD204B. Параметры режимов микросхемы программируются через четырехпроводной последовательный SPIинтерфейс и массив регистров управления внутри микросхемы.

### Борьба с шумами

Борьба с шумами улучшает параметры конвертера. Одной из значительных составляющих является шум, возникающий при одновременном срабатывании компараторов во flash АЦП. Повышенная разрядность используемых АЦП позволяет увеличить динамический диапазон сигнала и увеличить возможности для борьбы с шумами.

В режиме SNR Boost обеспечивает постоянное разрешение 9 разрядов. В этом режиме спектральная обработка сигнала в полосе пропускания 100 МГц обеспечивает спектральную плотность шума на уровне —152,0 dBFS/Гц. При этом допускается программное смещение центральной частоты полосы пропускания.

В режиме Bit Burst обеспечивается изменение разрешения от низкого (9 бит) до высокого (14 бит). Уровень плотности шумов в режиме высокого разрешения —152,7 dBFS/Гц. Конфигурация режима Bit Burst является программируемой и устанавливается пользователем.

Основные параметры при шумовой фильтрации:

- Для входного сигнала 150 МГц: -3 dBFS;

- SNR (SNR Boost) 71,6 dBFS;

- SNR (Bit Burst) 69,6 dBFS;

- · SFDR 88 dBFS;

- Non-HD2/HD3 SPUR -90 dBFS.

#### Определения характерных параметров

Signal To Noise And Distortion (SINAD) выражается в отношении дБ мощности входного сигнала к общей мощности всех других спектральных компонентов, включая гармонические искажения, но исключая постоянное смещение. SINAD обычно выражает отношение допустимой возможной синусоидальной мощности при полной шкале [dBFS] или относительную мощность реального сигнала несущей частоты [dBc].

Spurious Free Dynamic Range (SFDR) — отношение дБ мощности входного сигнала к мощности пиковых ложных сигналов, где ложным сигналом является любой сигнал в выходном спектре, который не присутствует во входном сигнале.

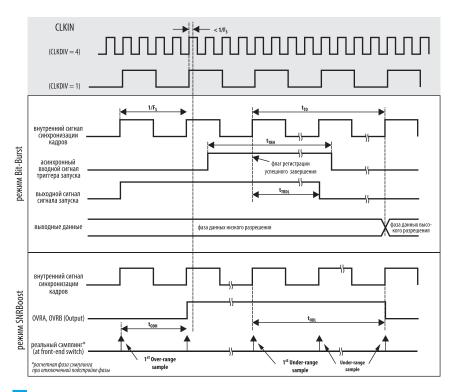

Ha рисунке 3 показаны временные диаграммы синхронизации преобразования для режимов SNR Boost и Bit Burst.

Рис. 3. Временные сигналы фаз синхронизации при работе микросхемы в различных режимах постобработки

#### Определения основных сигналов интерфейса JESD204D

DEVICE CLOCK — мастер-сигнал синхронизации, к которому привязаны вся структура фреймов и мультифреймовые сигналы синхронизации. Для микросхемы LM97937 этот сигнал привязан к CLKIN.

FRAME (кадр) состоит из последовательных октетов выходных данных, позиция каждого привязана к началу кадра.

FRAME CLOCK — сигнал синхронизации последовательности самих фреймов в потоке. Предназначен для мониторинга их положения при приеме. В микросхеме LM97937 этот сигнал генерируется от внутреннего синхрогенератора, и внешний сигнал не требуется.

SERIAL LANE — сигналы дифференциальной пары (физический уровень) для передачи данных в одном направлении.

LINK (DATA LINK) — тракт передачи, состоящий из части двух устройств: приемника и передатчика. LINK содержит часть передающего тракта LM97937 (передатчик) и со стороны приемника, FPGA или ASIC и соединительные трассы проводников между ними.

MULTI-FRAME — последовательность из ряда фрэймов.

LOCAL MULTI-FRAME CLOCK (LMFC) — сигнал мультикадровой синхронизации, позволяющий выделить нужный кадр из последовательности. Сигналы являются производными, синтезируются внутри самой микросхемы LM97937 и используются для синхронизации LINK [ESD204B.

ОСТЕТ — группа из восьми цифровых кодов, кодированных в коде 8/10 В.

SYSREF — периодический сигнал вставки или пропуска, предназначенный для выравнивания границ локальных мультикадров в тракте линка JESD204B subclass 1. SYSREF синхронизирован с сигналами внутренней синхронизации микросхемы.

SCRAMBLING — процесс рандомизации выходных данных по известному для передатчика и приемника закону. Основное назначение скремблирования — облегчить восстановление сигнала синхронизации на стороне приемника за счет устранения длинных последовательностей нулей или единиц в передаваемом потоке без изменения скорости передачи и введения избыточного кода.

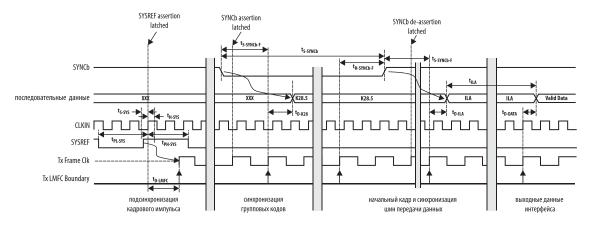

На рис. 4 приведены временные диаграммы интерфейса JESD204B.

Рис. 4. Временные диаграммы интерфейса JESD204B

При проектировании системы очень важно использовать корректную нагрузку и избегать скачкообразных изменений волнового сопротивления среды передачи, поскольку эти факторы могут оказывать существенное негативное влияние на передачу данных и привести к сбоям в работе канала между передатчиком и приемником JESD204B. Грамотное проектирование позволит исключить эти проблемы и гарантировать корректное функционирование системы.

На рисунке 5 показана топология и цоколевка микросхемы LM97937.

Рис. 5. Цоколевка сигналов микросхемы LM97937 в корпусе QFN-56

#### Режим SNR Boost

Технология SNR Boost позволяет уменьшить шум квантования и тем самым увеличить динамический диапазон выходного спектра за счет некоторого увеличения шума на краях спектрального диапазона, поскольку для большинства приложений эти

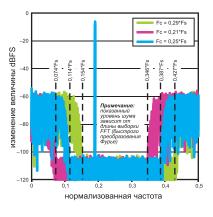

области обычно не являются рабочими. Когда микросхема сконфигурирована в режиме SNR Boost, в 54,6% полосы Найквиста увеличивается динамический диапазон сигнала. Это позволяет увеличить динамический диапазон примерно на 101 МГц при сэмплировании на скорости 370 МГц. SNR (отношение сигнал/шум) модуля Boost может иметь центральную область с уменьшенным шумом для частот 0,25\*Fs или 0,29\*Fs или 0,21\*Fs, как показано на рисунке 6.

Рис. 6. Формы шумового спектра в режиме SNR Boost для трех различных центральных частот

Изменение формы шума квантования воздействует также и на другие свойства шума, включая PAR (peakto-average ratio) и общий шум квантования.

#### Режим Bit Burst

Режим Bit Burst обеспечивает увеличение динамического диапазона посредством установки управляю-

щего бита High Resolution ADC на короткий период времени перед возвратом в состояние с 9-разрядным разрешением. Частота смены разрешения определяется скважностью и продолжительностью фазы High Resolution burst. Конфигурация битов установки High Resolution и длительность этого цикла программируется в управляющих регистрах. Длительность фазы High Resolution равна 2N сэмплов, где N может устанавливаться от 10 до 25. Длительность фазы Low Resolution равна 2Nx(1/k-1), где k определяет скважность цикла.

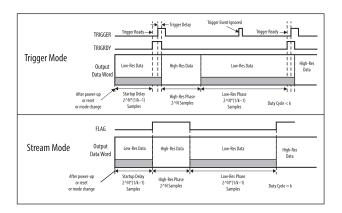

Режим Bit Burst имеет два подрежима: Trigger Mode (импульсный) и Stream Mode (потоковый).

В Trigger Mode биты высокого разрешения (High Resolution bits) становятся активными при переходе из низкого в высокое состояние управляющего входного сигнала TRIGGER. После инициации burst cycle по сигналу TRIGGER изменение сигнала TRIGGER игнорируется, пока не завершится burst cycle. Сигнал TRIGRDY становится низким после того, как TRIGGER индицирует, что burst cycle находится в работе, и переходит в логическое состояние «1», когда burst cycle завершается и новый цикл может быть запущен.

В режиме Stream Mode (поток) биты высокого разрешения становятся активными периодически, образуя непрерывный поток. Сигнал TRIGGER при этом игнорируется. Бит контрольного флага (Flag) индицирует статус данных в фазе burst. Когда бит Flag находится состоянии лог. «1», АЦП находится в фазе с высоким разрешением. И наоборот,

при лог. «0» АЦП имеет низкое разрешение. В режиме Stream скважность равна k, период High Resolution burst равен 2N/k.

Оба подрежима обеспечивают фазу низкого разрешения после включения питания и после программного сброса, а также при смене режимов. Во время этой фазы данные с низким разрешением поступают на выход со скоростью 2Nx(1/k-1) сэмплов, где N и к определяются по умолчанию в установочных регистрах (после включения питания) или текущими установками этих режимных регистров (после sleep mode, после программного сброса или после изменения режимов). На рисунке 7 показаны временные диаграммы работы в обоих режимах (Trigger Mode и Stream Mode).

Рис. 7. Диаграммы работы в различных режимах

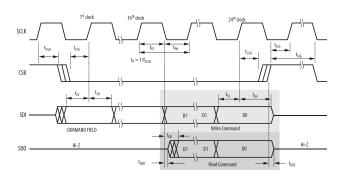

На рисунке 8 показана временная диаграмма управляющего интерфейса SPI.

Рис. 8. Временные диаграммы сигналов управляющего интерфейса SPI

#### Режимы Power Down и Sleep

Для уменьшения потребляемой мощности пользователь может активировать любой из двух режимов — Power

Down или Sleep — без выключения питания. Оба они позволяют в одинаковой степени уменьшить потребление. Различие только во времени перехода в нормальный режим: при переходе из Power Down в нормальный режим производится еще и калибровка АЦП, которая занимает определенное время, а после «просыпания» калибровка АЦП не выполняется.

Установка режимов производится через установку битов в режимных регистрах.

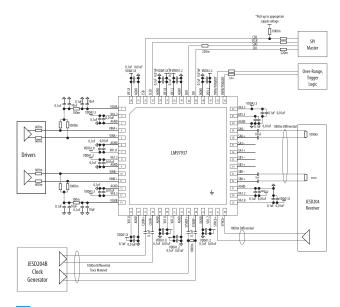

Power Down может быть включен в любое время. На рисунке 9 показана типовая схема включения микросхемы LM97937.

Рис. 9. Типовая схема включения микросхемы LM97937

# Отладочный набор LM97937EVB

При разработке собственного приложения на базе микросхемы LM97937 разработчикам будет очень полезен отладочный набор LM97937EVM (рис. 10), который позволяет оценить работу микросхемы LM97937 в условиях реальных сигналов и режимов пользователя.

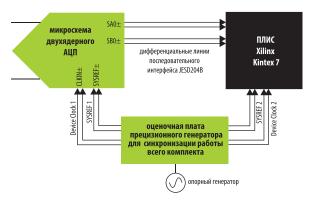

Рис. 10. Структура отладочного набора для LM97937

Отладочная плата LM97937EVM содержит саму микросхему LM97937 с необходимыми разъемами и интерфейсами, ПЛИС Xilinx серии Kintex 7 (для реализации пользовательского приложения) и генератор системной синхронизации LKM04828 для интерфейса JESD204B.

Отладочный модуль EVM имеет трансформаторы для гальванической развязки аналоговых сигналов, что обеспечивает широкий диапазон для использования различных источников входного сигнала с различным частотным диапазоном. Модуль LMK04828 размещен на EVM и может быть дополнительно сконфигурирован для обеспечения сигнала синхронизации SYSREF с очень низким джиттером и улучшения параметров работы АЦП и полной поддержки работы интерфейса JESD204B subclass 1.

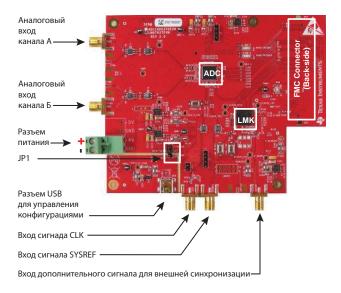

Внешний вид оценочной платы показан на рисунке 11.

Рис. 11. Внешний вид оценочной платы EVM97937

Отладочная плата включает следующие компоненты:

- развязывающие трансформаторы для аналоговых входов и сигнала синхронизации с полосой пропускания от 5 МГц до 1 ГГц;

- системный генератор опорной частоты LMK04828 для синхронизации работы интерфейсов ПЛИС, который может использоваться также и для сэмплирования АЦП;

- FMC-коннектор для интерфеи́са JESD204B;

- доступ к управляющему интерфейсу осуществляется от компьютера через интерфейс USB и микросхему конвертера интерфейсов FTDI USB-to-SPI.

Цифровой поток данных от платы LM97937EVM может быть легко подключен к другой оценочной плате захвата—TSW14J56EVM. Модуль TSW14J56EVM обеспечивает прием и захват данных, передаваемых через высокоскоростной интерфейс JESD204B. Плата захвата обеспечивает декодирование потока и сохранение данных кадров информации в памяти. Анализ данных производится в дальнейшем компьютером, куда транслируется через интерфейс USB файл с информацией. Обработка и анализ производятся в компьютере с помощью специальной программы High Speed Data Converter Pro (HSDC Pro).

Параметры LM97937 и LMK04828 устанавливаются посредством простого программного графического интерфейса пользователя, который обеспечивает пользователю быстрый и удобный способ изменения конфигурации всего устройства.

LM97937EVM непосредственно подсоединена к модулю TSW14J56EVM аппаратного захвата данных через высокоскоростной FMC-коннектор и может быть опционально подключена к платформе КС705 обработки на ПЛИС Xilinx. Для поддержки работы комплекса обработки доступно программное обеспечение The High Speed Data Converter Pro, которое обеспечивает захват и анализ данных при использовании TSW14J56EVM.

#### Основные параметры отладочного модуля

- Гибкое трансформаторное сопряжение аналогового сигнала и сигналов синхронизации позволяет использовать различные источники входных сигналов с различным диапазоном рабочих частот.

- С помощью прилагаемого программного графического обеспечения обеспечивается простота и легкость конфигурирования параметров LM97937, LMK04828 для различных режимов работы. Управление производится через USB-порт компьютера.

- Программное обеспечение High Speed Data Converter Pro позволяет быстро и эффективно проверить и оценить все возможности АЦП.

- Обеспечивается простое подсоединение к модулю TSW14J56EVM захвата данных или же прямое соединение через коннектор FMC к набору разработчика на основе ПЛИС Xilinx.

# Комплект разработчика

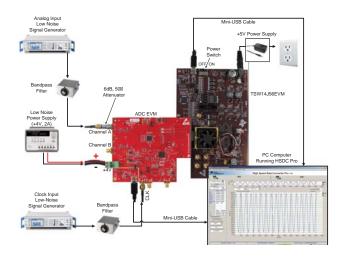

На рисунке 12 показана структурная схема и примерные типы оборудования, позволяющие на базе оценочной платы LM97937 EVM создать рабочее место для разработки пользовательского ПО, а также для проведения исследовательских работ в полном объеме.

В состав комплекта разработчика входит следующее оборудование:

• отладочная плата (EVM);

Рис. 12. Комплект разработчика на базе отладочных наборов и специализированного ПО

- два mini-USB кабеля;

- ВЧ-генераторы аналоговых сигналов и сигналов синхронизации;

- оценочная плата захвата TSW14J56EVM;

- источники питания для оценочных плат;

- блоки полосовых фильтров;

- персональный компьютер, работающий под ОС Windows XP/7/8;

- программное обеспечение для просмотра и анализа выходных данных с графическим интерфейсом пользователя.

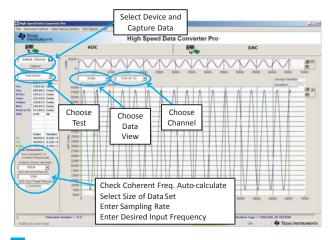

Рис. 13. Графический интерфейс программы High Speed Data Converter Pro

Рекомендации по укомплектованию полного набора разработчика приведены в руководстве [1]. Подробная информация по остальным компонентам набора разработчика приведена также в списке литературы.

На рисунке 13 показан вид рабочего окна графического интерфейса ПО High Speed Data Converter Pro. Программа HSDP загружается с сайта компании ТІ. Работа с отладочным набором и установка ПО довольно подробно описаны в источнике [1].

# Литература

- LM97937EVM R2 User's Guide. SLU542 Texas Instruments. December, 2013.

- 2. JESD204B Outputs. Texas Instruments. January, 2014.

- 3. JEDEC Standard JESD204B (July, 2011). JEDEC Solid State Technology Association. www.jedec.org

- 4. Using Clock Jitter Analysis to Reduce BER in Serial Data Applications. Application Note 5989-5718EN. Agilent Technoloiges. December, 2006.

- 5. Measuring in Digital Systems. Application Note 5988-9109EN. Agilent Technologies. January, 2008.

- 6. LM97937 Datasheet. TI literature number SNVS990.

- 7. TSW14J56EVM User's Guide. TI literature number SLWU086

# СПЕЦПРЕДЛОЖЕНИЕ!

Компания РТ Electronics предоставляет бесплатный отладочный набор LM97937EVM + TSW14J56EVM (см рис. 12)

Скоростной АЦП LM97937 до 14 бит 370 МГц без лицензии

Отладочные платы на складе в Санкт-Петербурге